Das College of Engineering der Seoul National University gab bekannt, dass ein Forschungsteam unter der Leitung von Professor Lee Cheol-ho vom Fachbereich Elektrotechnik und Informatik eine umfassende Roadmap zum Thema „Gate Stacking“ entwickelt hat. Als Kerntechnologie für zweidimensionale (2D) Transistoren rückt Gate Stacking in den Fokus der Halbleiterbauelemente der nächsten Generation. Die Forschungsergebnisse wurden in der Fachzeitschrift Nature Electronics veröffentlicht.

Derzeit basieren die meisten Halbleiter auf siliziumbasierter CMOS-Technologie. Mit dem Vordringen in den Subnanometerbereich treten jedoch zunehmend physikalische und elektrostatische Einschränkungen in den Vordergrund. Zweidimensionale Halbleiter, deren elektrische Eigenschaften auf atomarer Dicke erhalten bleiben, gelten als Kanalmaterialien, die Silizium übertreffen. Sie haben die Aufmerksamkeit führender globaler Halbleiterunternehmen wie Samsung und TSMC auf sich gezogen und wurden in die Roadmap für die Post-Silizium-Technologie aufgenommen. Die größte Herausforderung für die Kommerzialisierung zweidimensionaler Halbleiter stellt jedoch die Gate-Stack-Integrationstechnologie dar, deren Qualität sich direkt auf die Leistung und Stabilität des Geräts auswirkt.

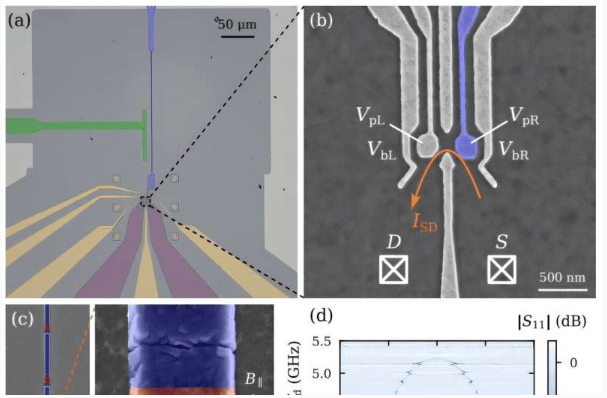

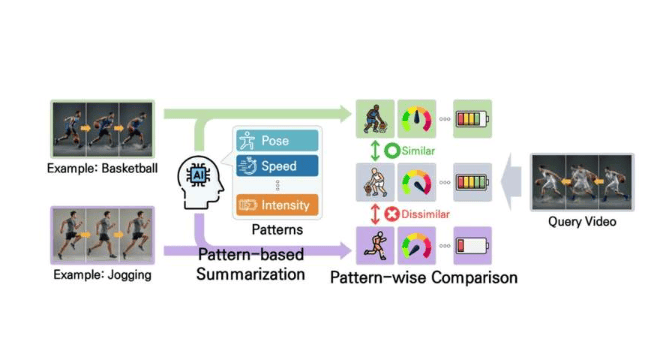

Das Team von Professor Li Zhehao analysierte verschiedene Gate-Stack-Integrationsmethoden und führte ein quantitatives Benchmarking anhand von Leistungskennzahlen wie Schnittstellenfallendichte und äquivalenter Oxiddicke durch. Die Studie kategorisierte die Gate-Stack-Integrationsmethoden in fünf Kategorien und verglich sie mit den Zielen der International Roadmap for Devices and Systems (IRDS), wodurch ein systematischer Entwicklungsfahrplan entstand. Darüber hinaus demonstrierte die Studie das Potenzial der ferroelektrischen Gate-Stack-Technologie für Geräte der nächsten Generation und betonte die Machbarkeit praktischer industrieller Anwendungen, einschließlich Anforderungen wie Back-End-of-the-Line-Kompatibilität (BEOL) und Niedertemperaturabscheidung.

Diese Forschung liefert nicht nur eine Blaupause für die Entwicklung von Halbleitern der nächsten Generation, sondern demonstriert auch die Machbarkeit von Transistoren mit extrem niedrigem Stromverbrauch und hoher Leistung und schlägt konkrete technische Richtungen für die monolithische dreidimensionale Integration und BEOL-kompatible Prozesse vor. Professor Li sagte: „Die Realisierung hochwertiger Gate-Stacks ist der Schlüssel zur Kommerzialisierung zweidimensionaler Transistoren. Diese Forschung liefert eine Standardblaupause zur Bewältigung dieser Herausforderungen und hat erhebliche Auswirkungen auf Wissenschaft und Industrie.“

Weitere Informationen: Yeon Ho Kim et al., Gate stack engineering for two-dimensional transistors, Nature Electronics (2025). Zeitschrifteninformationen: Nature Electronics