Die Entwicklung von KI-Systemen steht heute vor der Herausforderung der Skalierung. Um einen schnellen Datenaustausch zwischen den Prozessorchips zu gewährleisten, werden enorme Speichermengen benötigt. Herkömmliche GPUs, die ursprünglich nicht für KI-Modelle konzipiert wurden, benötigen mehrere GPUs, die über Hochgeschwindigkeitsnetzwerke verbunden sind, um große Sprachmodelle (LLMs) zu unterstützen. Dies führt zu langsamen Datenübertragungsraten und hohem Energieverbrauch.

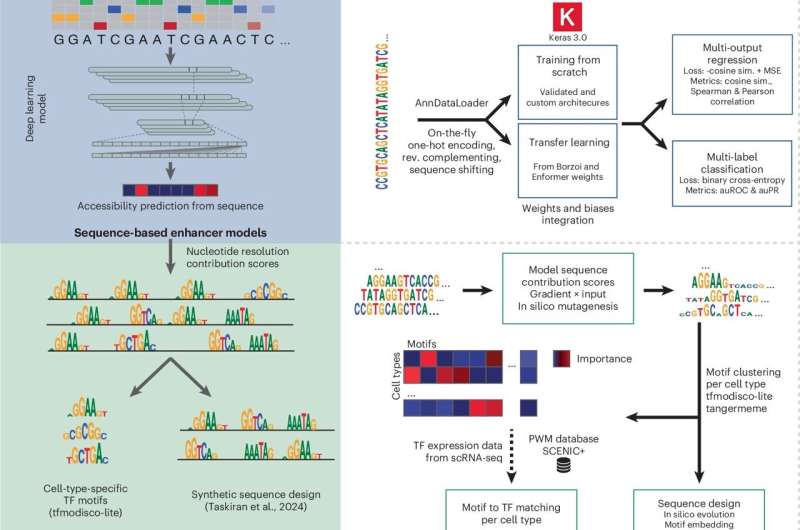

Um den GPU-Flaschenhals zu überwinden, haben Unternehmen wie Cerebras in Kalifornien Wafer-Level-Prozessoren entwickelt. Diese Chips sind groß und verfügen über enorme Mengen an On-Chip-Speicher sowie Hunderttausende von Kernen. Wafer-Level-Chips allein reichen jedoch nicht aus; es werden auch spezialisierte Softwaresysteme benötigt. WaferLLM, entwickelt in Zusammenarbeit zwischen der Universität Edinburgh und Microsoft Research, zielt darauf ab, große LLMs effizient auf Wafer-Level-Chips auszuführen.

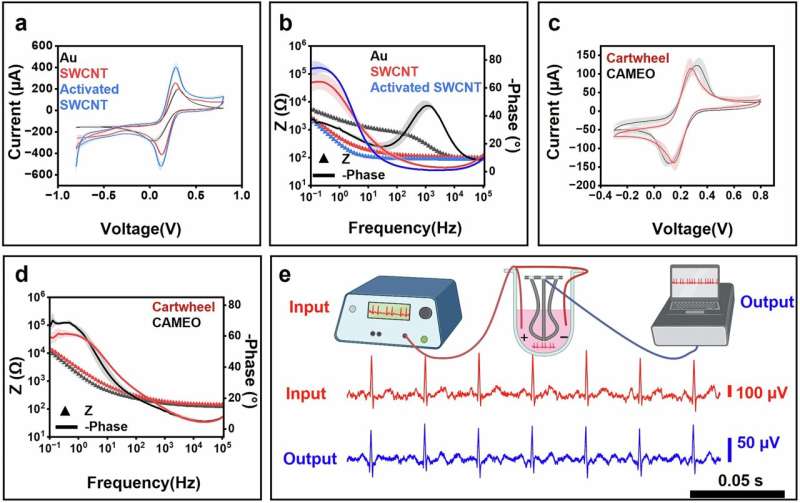

WaferLLM nutzt drei neue Algorithmen, um große mathematische Operationen in kleinere Teile zu zerlegen. Dadurch können benachbarte Kerne diese gemeinsam verarbeiten, wobei die Informationen lokal übertragen werden, um die durch die Kommunikation über große Entfernungen verursachte Verlangsamung zu vermeiden. Gleichzeitig wird eine neue Strategie eingeführt, um verschiedene Teile des LLM auf Hunderttausende von Kernen zu verteilen und Verarbeitung und Kommunikation zu koordinieren, um einen effizienten Chipbetrieb zu gewährleisten. Diese im Edinburgh International Data Center getesteten Anpassungen führten zu einer etwa 100-fach schnelleren Textgenerierung auf Wafer-Level-Chip-Ebene, einer zehnfach geringeren Latenz und einer doppelt so hohen Energieeffizienz im Vergleich zu einem Cluster aus 16 GPUs.

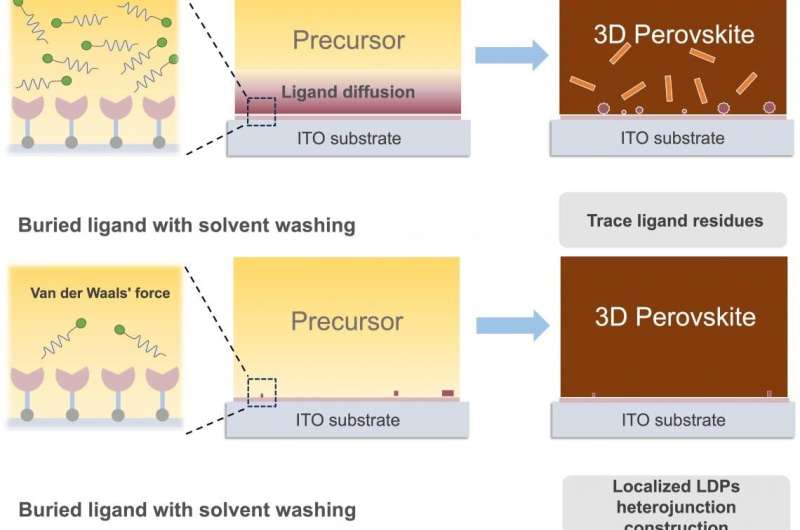

Während GPUs über ein ausgereiftes Software-Ökosystem verfügen, eignen sich Wafer-Level-Chips besser für Workloads, die auf extrem niedrige Latenz, extrem große Modelle oder hohe Energieeffizienz angewiesen sind. Gleichzeitig entwickelt sich die GPU-Technologie stetig weiter. Daraus folgt, dass die KI-Infrastruktur zu einem Co-Design-Problem wird, das eine parallele Weiterentwicklung von Hardware und Software erfordert. Die Überarbeitung des Software-Stacks ist entscheidend, um die nächste Generation der KI-Leistung zu erschließen. Für die Öffentlichkeit werden KI-Systeme mehr Anwendungen unterstützen, die zuvor langsam oder kostspielig waren, und der Übergang zum Wafer-Level-Computing markiert eine neue Phase in der KI-Entwicklung.